# 導電性DLCコーティングの 半導体検査用プローブへの応用

近年、電子機器の高機能化や小型化にともない、搭載される半導体素子のパッケージサイズも小型化、薄型化が進んでいる。しかしながら、出荷前の最終検査手法は半世紀以上変わらず、半導体検査プローブ(プローブ)を半導体パッケージ端子(端子)へ接触させ、電気特性を測定することで良否を判定している。しかし、プローブがパッケージサイズに合わせて小型、低荷重化すると、端子との接触面積が小さくなるため、電気的な接触が不安定になる。また、わずかな接触不良で不良判定となり、プローブ先端のクリーニングによる半導体検査装置の稼働率低下や再検査によるコストアップなどにつながる。そのため、端子とプローブを電気的に安定して接触させることは半導体最終検査にとって重要である。このようなニーズに応えるべく、当社ではお客さまから支給されたプローブにスパッタリング法によって導電性のダイヤモンドライクカーボン膜(DLC膜)を形成したC3コーティング( $\underline{C}$ onductive  $\underline{C}$ arbon  $\underline{C}$ ontact)サービス事業を2009年より行っている。本稿では、C3コーティングについて紹介する。

ターゲット事業本部

廣瀬 研太

## D-1 概要

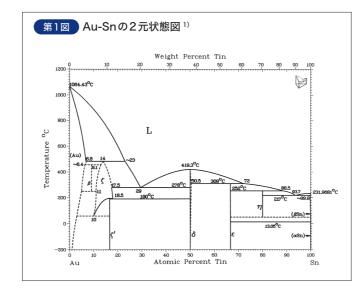

半導体検査装置の稼働率低下、すなわちプローブと端子の電 気的な接触を不安定にするプローブ側の要因は3つ考えられる。 1つ目はプローブが内蔵するスプリング機構など機械的な接触の 安定性であり、プローブ仕様やソケットの加工精度、構造に依存 し、日々改善が進められている。2つ目はプローブ先端形状の変化 であり、端子材との接触による摩耗やプローブ先端のクリーニング により生じることから、プローブ寿命にも関わる。3つ目は端子材の 転写等であり、とくにPbフリーはんだやSnめっきが端子に使われ る製品では、端子素材の主成分であるSnがプローブに転写する。 転写したSnの酸化によりプローブの接触抵抗値にばらつきが現 れ始め、不良判定が頻発することで、プローブ先端のクリーニング や交換、さらには不良判定した製品の再検査を要する。その結果、 半導体検査装置の稼働率低下や再検査コストの増大の原因とな る。半導体検査プローブ先端の主要な材料である金めっき(Au) はAu-Snの2元状態図で示すように(第1図)、転写するSnとさま ざまな温度・組成で種々の金属間化合物をつくることが知られて いる。そのため、転写したSnは簡単に取り除くことができない。一 般的には研磨により転写したSnをプローブめっきのAuとともに 削り取ることでAuめっきを露出させて使用を続けるが、研磨して も歩留まりが回復しなくなるまで使用を続けると、プローブの先端 は基材(鉄系あるいは銅合金など)まで露出することがある。これら 3つの要因は1つでも生じると相互に影響し、接触不良につがる。 しかし、出荷前の最終検査において、端子とプローブが接触するこ とは避けられず、Sn転写に対して根本的な解決手段は見出されて いない。そのため、接触の安定にはSn転写の抑制と先端形状の 維持が最も重要な課題として認識されている。

この課題に対応するため、当社では、プローブに導電性のDLC 膜を形成するC3コーティングサービス事業を行っている。半導体 検査プローブにDLC膜を適用するのは、主成分の炭素(C)とSnが化合物を生成しないためであり、はんだと接触してもSnが転写(合金化、付着)しにくい。また、プローブに適用される通常のAuめっきにくらべて、はるかに硬質で摺動性が高いため、接触が長期的に安定し、耐久性に優れる。一方、一般的なDLC膜は $10^{7}\sim 10^{14}\Omega\cdot \text{cm}$ と高い電気抵抗率を示し、絶縁性の材料である。そのため、半導体検査プローブにDLC膜を適用するには、導電性を付与すること、プローブ先端のめっき(金、パラジウム等)との密着を確保すること、および組立後のプローブ完成品に成膜できることが必要であり、これら全ての要件を満たすことで、DLC膜が半導体検査プローブ用のC3コーティングとして機能する。

## D-2 プローブへのC3コーティングの適用

C3コーティングの成膜方法は、物理蒸着法(PVD法: Physical Vapor Deposition)の一つであるスパッタリング法をもちいる。ほ かにDLC膜の成膜方法として、化学蒸着法(CVD法: Chemical Vapor Deposition)やアークイオンプレーティング法などがもちい られるが、微細なプローブ先端に平滑で緻密な膜を成膜できるこ と、導電性成分を添加することができること、プローブに搭載され るバネ荷重に影響しない低温での成膜が可能で完成品のプロー ブへ直接成膜できることから、スパッタリング法を選択している。ま た、DLC膜は緻密で高硬度な膜を形成するほど膜応力が高く、プ ローブの先端のような微細な箇所へ成膜すると剥離が生じること があるが、C3コーティングはDLC膜とプローブのAuめっきの間 に密着層を設けることで膜応力を下げ、半導体検査に耐える密着 力を確保している。第2図にコーティング例を示す。C3コーティン グは、支給されたプローブにコーティングを施すことでプローブの 機械的な接触安定性はそのままに、主成分のCでSn転写を抑制 し、DLC膜の高硬度による先端形状維持と摺動性と平滑性により Sn剥離の効果(自浄作用)が期待でき、長期間の接触安定化、プ ローブの長寿命化の実現するものと考えられる。

## D-3 C3コーティングの各種性質(または物性)

### 3.1 C3コーティングの電気的性質

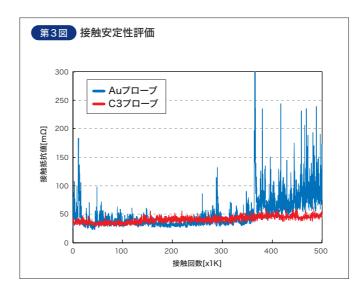

C3コーティングの接触安定性評価のため、Snリード端子を模擬したSnめっきプレートへの連続接触により接触抵抗値測定を行った。相手端子材は銅合金に純Snめっきしたプレートとし、従来のAuめっきしたAuプローブとC3コーティングしたC3プローブを比較評価した。測定は、プローブに接触ごとに100mAを通電し、Snめっきプレートとプローブ先端の接触箇所を変えることで、毎回新たなSnめっき表面へ接触させ、実際の出荷前の最終検査に近い状態を模擬した。また、Sn転写を促進するためSnめっきプレートを85℃に加熱し、100コンタクト(接触)ごとに接触抵抗値

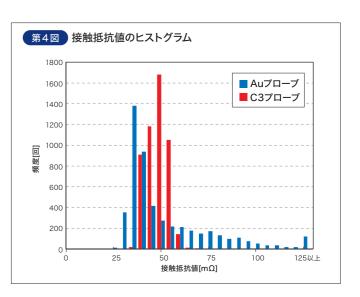

を測定した。測定結果を第3図に示す。Auプローブは初期から接触抵抗値のばらつきがみられ、35万回を超えると上昇および変動がみられるが、<math>C3プローブでは変動は小さく、その上昇はわずかである。また、データをヒストグラムにした結果を第4図に示す。<math>Auプローブでは頻度のピーク位置が35mΩであるが、高抵抗値側に分布の広がりがみられ、大きく分散している。一方、<math>C3プローブは頻度のピーク位置が45mΩとAuプローブに比べわずかに高いが、ピーク高さは<math>Auプローブより高く(頻度が多く)、分散が小さいことから、安定した接触抵抗値が得られていることがわかる。これがC3 コーティングの最大の特長である。

### 3.2 C3コーティングの物理的性質

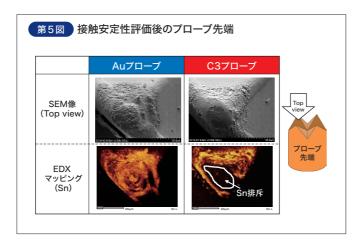

連続コンタクト試験後の2種類のプローブ先端について、SEM 観察およびSnのEDXマッピング結果を第5図に示す。Auプロー ブでは、頂点一様にSnが検出され、Snが付着した部分では表面 粗さが増加している。一方、C3プローブは頂点にSnが検出されな い領域がみられ、Auプローブで見られたような表面形態の粗さは みられず、プローブ先端形状が維持されている。このように、C3 コーティングによってSn転写の抑制と先端形状維持の効果が得 られていることがわかる。これらの効果の詳細については、次項以 降で説明する。

## D-4 C3コーティングのセルフ・クリーニング効果

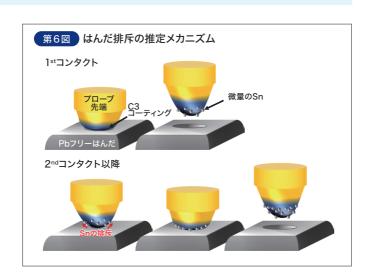

第6図にC3コーティングのはんだ排斥の推定メカニズムの模 式図を示す。はんだにプローブ先端が突き刺さると、プローブ先端 のはんだ接触箇所には微量のSnが一時的に付着・残留する可 能性がある。2回目以降のコンタクトでは、プローブ先端が突き刺 さる際に、1回目に付着した微量のSnが先端から剥離され斜面部 に排斥される。これを繰り返すことではんだは先端から排斥され、 第5図のEDXマッピングのような特徴的な残留Sn分布となる。こ れをセルフ・クリーニング効果と呼んでいる。この効果により、C3 コーティングでは、長期間接触が安定し、プローブの長寿命化を 実現することが可能となる。

## D-5 C3コーティング活用のための注意点

半導体検査プローブは半導体パッケージのタイプに応じた多種 多様なものがあり、その全てにおいてC3コーティングが万能とい うわけではない。C3コーティングの課題を理解すれば、適用の幅 を広げることができ、またC3コーティングのはんだ排斥の効果を さらに高めることも期待できる。DLC膜が持つ高い硬度とはんだ 成分(Sn)の転写抑制の特長をもつが、本来絶縁性の材料という こともあり、導電性を付与しても膜の比抵抗値は金属膜に対し1 ~2桁高い。コーティングの際の膜は薄いため抵抗値は低いが、プ ローブの使用状況によっては、これが問題として顕在化する場合 があるので注意が必要である。

### 5.1 C3コーティングの硬質端子への適用性

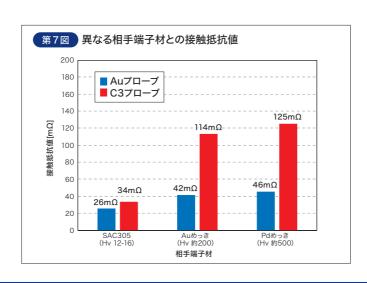

相手端子材の材種を変えて測定した接触抵抗値を第7図に示 す。相手端子材は①Pbフリーはんだ(Sn-3.0Ag-0.5Cu:SAC305)、 ②Auめっきプレート(CuプレートにAuめっき)、③Pdめっきプ レート(CuプレートにPdめっき)とし、C3コーティングしたプロー ブと従来のAuめっきプローブ(未処理)を各端子材に接触させ、

荷重25gfが得られる適正ストローク量0.65mm時の接触抵抗 値を取得した。未処理のAuめっきプローブ、C3プローブともに、 Pdめっきプレートの抵抗値>Auめっきプレートの抵抗値>鉛

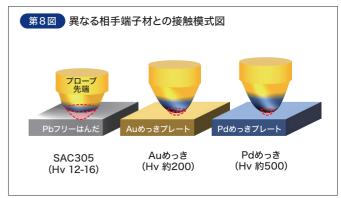

フリーはんだプレート、の抵抗値の傾向を示した。しかしながら、 C3プローブでは、Pdめっきプレート、Auめっきプレートが相手 の接触抵抗値が、Pbフリーはんだ相手のそれよりも顕著に接触 抵抗値が高くなることが確認された。相手材により高い接触抵抗 が観測される理由は、AuめっきプレートとPdめっきプレートは、 Pbフリーはんだプレートにくらべて硬質のため実効的な接触面積 が減少するためと考えられる。第8図にプローブの相手材ごとの接 触時の模式図を示す。各端子材のビッカース硬度から、ビッカース 圧子による圧痕の表面積の比率は、Pdめっき: Auめっき: はん だ=1.0:2.5:35.7となるが、プローブとの接触においても同様 の接触面積の差が生じるものと考えられる。Pbフリーはんだは、 AuめっきやPdめっきにくらべて柔らかく、ビッカース硬度で一桁 程度小さい。接触面は大きく塑性変形し、実効的な接触面積は広 くなる一方、相対的に硬質なAuめっきにプローブが接触しても変 形は小さく実効的な接触面積は小さくなる。このとき、プローブ先 端がAuめつきの場合は比抵抗値が小さいため、接触抵抗値の上 昇はわずかであるが、比抵抗値の高いC3コーティングの場合、接 触抵抗値が上昇する。これは、硬度の高い端子材に対して同じ先 端形状のプローブを適用した場合、C3コーティングは実効的な接 触面積が小さくなり膜比抵抗の高さが顕在化するからである。そ のため、硬質な相手材に対しては、プローブ先端を丸くすることや、 多頂点にして実効的な接触面積を増やす工夫が有効である。

### 5.2 C3コーティングに望ましいプローブ先端形状

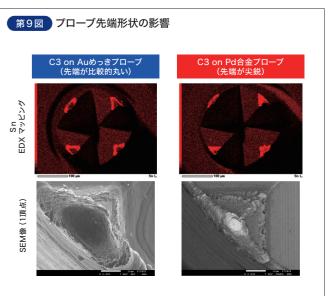

第9図に、Snめっきプレートに85℃、10万回コンタクトさせた 後のプローブの先端を観察した結果を示す。この時、先端が比較 的丸いAuめっきプローブにC3をコーティングしたものと、先端が 尖鋭なPd合金プローブにC3コーティングしたものを比較した。 C3コーティングしたAuめっきプローブでは4頂点全てでSnが排 斥されたプローブ表面となっているのに対し、C3コーティングした Pd合金プローブでは左下の頂点を除き先端までSnが検出され ている。SEM像を比較すると先端の丸みが違っており、頂点部の 面積に差があることがわかる。はんだの排斥は主に頂点の比較的 丸い場所(φ20μm程度の領域)でみられ、C3コーティングした Pd合金プローブも左下の頂点のごくわずかな領域(φ5μm程度 の領域)ではんだ排斥を確認できる。C3コーティングを適用するこ とで、低い接触抵抗値で安定させるのに有効な形状は、はんだ排 斥の領域を広く確保できる先端が比較的丸いプローブが望ましい

第10図にC3コーティングの種類を紹介する。当社では、さまざ まな用途に幅広くC3コーティングを適用できるよう、4つのグレー ドを商品化している。

| グレード                     | グレードの<br>説明と特徴     | 主な用途                                                                                |

|--------------------------|--------------------|-------------------------------------------------------------------------------------|

| グレードR<br>(汎用グレード)        | ・標準グレード            | ・はんだ端子のIC向け全般                                                                       |

| グレードC<br>(低抵抗グレード)       | ・低抵抗<br>・斜面部の平滑性向上 | ・低荷重プローブ(WLCSP向けなど)<br>・Pd 合金プローブとの組み合わせ                                            |

| グレードE<br>(酸化抑制)<br>グレード) | ・膜表面の酸化抑制          | ・長時間(60秒以上)テスト<br>(メモリ、SLT(System Level Test)など)<br>・硬質端子(非はんだ端子)<br>…Auめっき端子、PPFなど |

| グレードB<br>(非磁性グレード)       | ・非磁性               | ・磁気センサーテストなど                                                                        |

第10図 C3コーティングのグレード

本稿では、半導体検査プローブ先端へのSnの転写と先端形状変化に対するソリューションとして、C3コーティングの特長と有効に 活用するための注意点について紹介した。C3コーティングは、Pbフリーハンダ端子や純Snめっき端子の半導体パッケージの電気特性 検査において有効な方策であり、さらに装置稼働率の改善に寄与するものと考える。

参考文献 \*1) Thaddeus B. Massalsky: The Materials Information Society