# 次世代半導体を支える3D実装技術とその評価法

昨今の半導体分野では高性能化、高速化の要求 が年々増してきており、その要求にこたえるべく、 ムーアの法則に基づき、半導体の高集積率化、微 細化、低コスト化へと技術革新を進めてきた。

しかしながら、現状の技術では回路の微細化に ついて限界を迎えつつあるため、チップを積み上げ る3D実装や水平方向に実装する2.5D実装と いった新たな実装技術が普及しつつある。

これらの部品の3D実装には新規の接合技術が 数多く使われており、それにともない、新たな分析 評価技術が求められている。

本稿では3D実装、2.5D実装基板の評価、解析

物理解析センター 技術部 物理ソリューション室

物理解析センター 椋木 新也

物理解析センター 解析部 関門解析室

寛侑

手法をメインに、半導体デバイスやパワーデバイスなど、さまざまな実装部品における、剥がれ、クラック、破壊、変形などの不具

合品調査や試作品の評価に対して、多種多様なメニューの中から特徴のある解析メニューについて紹介する。

# A-1 パッケージの進化(3D、2.5D 実装)に求められる設計

チップレット(第1図)は、チップ内のグローバル配線の一部を 配線基板側に持たせることで、積層されたチップ間の通信を効 率的に行うためにシステム設計されたものである。その設計には、 インターポーザーやサブストレートなどのVia(ビア: 貫通孔)お よび銅配線の微細化と信頼性、高密度実装における歩留まり、 放熱経路や応力の複雑化、電気特性などの機能試験を考慮した

構造と解析手法が必要である。

また、ハイエンドの半導体では、Chip-to-Wafer方式のハイブ リッド接合をもちいた製品開発も進んでおり、接合面の各種活性 化処理、Cu電極やSiO2界面における接合強度、狭ピッチ絶縁 性、低温接合性、反りなどを考慮した設計が必要である。

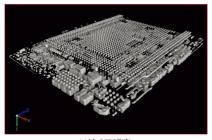

# 第1図 3次元実装部品のX線CT観察および断面観察の事例

X線CT観察

# A-2 Via接合部における断面解析

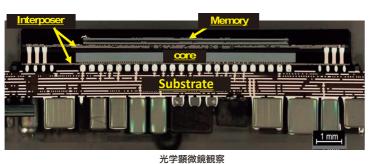

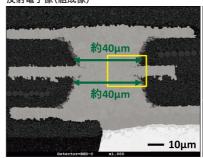

第2図はサブストレート内の約70μm径のVia接合部の中心 部を横断する形で断面試料を作製し観察したもので、銅配線と Viaの接合界面に黄色矢印で示すようなボイドが点在している。

このようなVia接合部に微細ボイドや剥離、クラック等の異常

が存在すると断線につながる可能性があり、機器故障や誤動作 の原因となる。そのため、接合状態を正確に把握しておくことが重

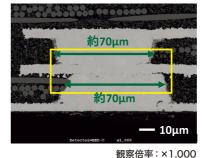

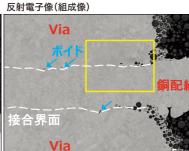

第3-1図はインターポーザー内のひとまわり小さい約40µm

# 次世代半導体を支える3D実装技術とその評価法 Technical Report A

径のマイクロVia中央部の断面観察結果である。 サブストレートのViaと同様、接合状態の把握が重要になる

が、この拡大写真からは一見、界面のボイドはほとんど無いもの と判断される。

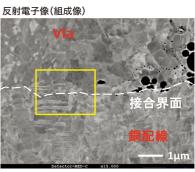

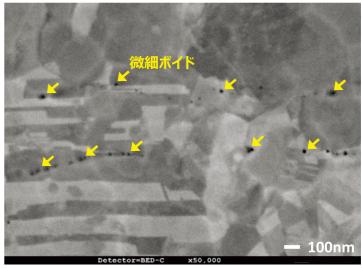

しかしながら、第3-2図に示すとおり、さらに5万倍まで拡大

すると、界面には帯状に分布するナノオーダーの微細ボイドが多 数認められる。このように年々縮小する複数のマイクロViaの中 央を狙って加工し、観察することには、高度な断面加工技術が必

# 第2図 サブストレート内のVia接合部の断面SEM観察

## 反射電子像(組成像)

反射電子像(組成像)

観察倍率:×5.000

# 第3-1図 インターポーザー内のマイクロ Via 接合部の断面 SEM 観察

反射電子像(組成像)

観察倍率:×1,000

観察倍率: ×5,000

観察倍率:×15,000

# 第3-2図 インターポーザー内のマイクロ Via 接合部の拡大観察

# 反射電子像(組成像)

観察倍率:×50,000

# Technical Report A 次世代半導体を支える3D実装技術とその評価法

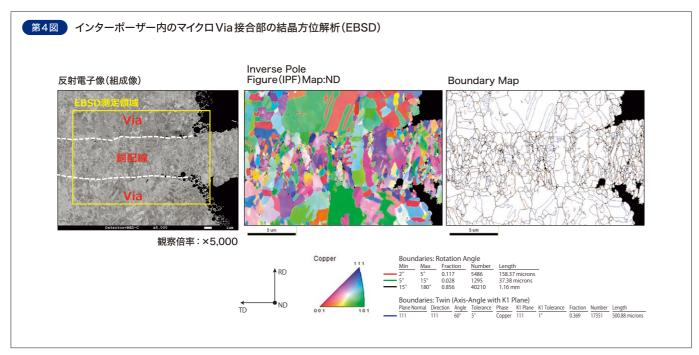

第4図に示す結晶方位解析 (Electron Back Scatter Diffraction: EBSD)により、界面付近の結晶方位や結晶粒の 情報を明確に得ることができる。Inverse Pole Figure (IPF) Mapでは結晶方位を色別で表示しており、Boundary Mapで は双晶や亜粒界を含む結晶粒界の情報を示している。

EBSD解析と断面 SEM (Scanning Electron Microscope: 走査型電子顕微鏡)観察結果より、微細ボイドの存在位置が特 定され、Via接合部に関しては、接合界面に対して結晶粒が連続 的に成長した状況から良好な接合状態が示唆される。

第5図はマイクロVia部断面のSecondary Ion Mass Spectrometry(SIMS)分析を行った結果である。SIMS分析で

はppmオーダーのごく微量元素の分析を行うことができ、空間 分解能1ミクロン以下での高精細マッピング分析が可能である ことから、本件のマイクロViaのような局所領域での分析に有効 である。

本分析では黄色丸を付けた箇所に注目すると、無電解めっき 層にはNa, N, S, Cl, B, Niがごく微量存在していることが明ら かとなり、ボイド生成との関連性が示唆されるデータが得られた。

このように、断面観察による、直接的な接合の良、不良の判断、 EBSD解析による結晶構造学的な考察、SIMSによる界面不純 物の把握を行う事によって、接合強度の改善や、微細ボイドの低 減による信頼性の向上につなげることができる。

# 第5図 インターポーザー内のマイクロ Via 接合部の SIMS 分析 反射雷子像(組成像 銅配線/Via界面付近にNa、N、S、CI、B、Ni元素が分布。

# A-3 2.5D 実装の各種接合評価

2.5D 実装については、インターポーザーの素材によって、多種 多様な方式が提案されている。具体的なインターポーザーの材 料としてシリコン(Si)、有機樹脂、ガラスなどがあげられ、丸形の ウェハーサイズ、角型のパネルサイズなどのバリエーションがあ る。それぞれメリット、デメリットがあり、たとえば、Siインターポー ザーよりも有機樹脂やガラスのほうが安価だが、微細配線には 限界がある。高周波特性は有機樹脂が良いが、Siチップとの線 膨張係数のミスマッチが問題になりやすいなどと言われている。

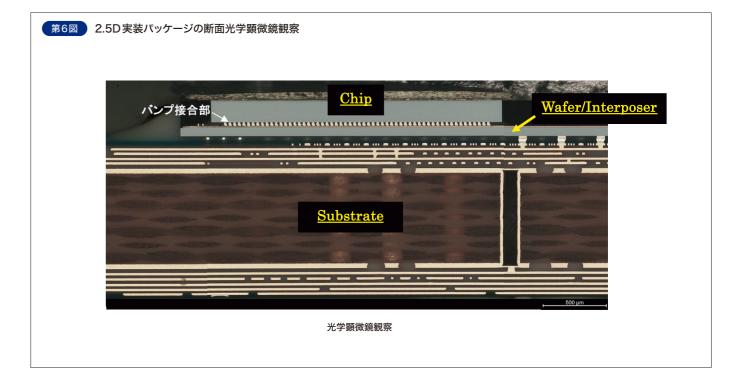

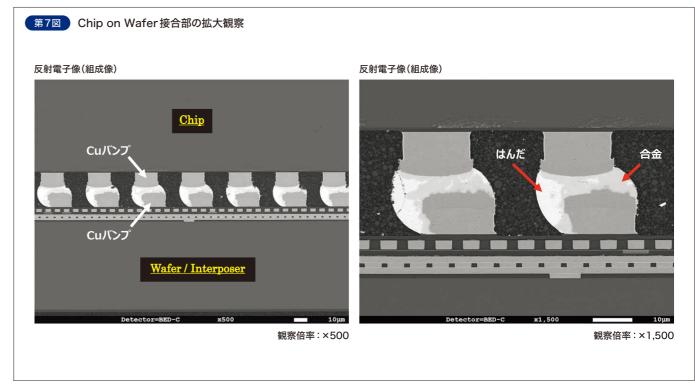

このような状況の中、開発競争が激化しており、重要になるのが 評価技術である。対象材料ごとに評価の観点や、必要なテクニッ クが異なるため、分析技術についても、日々進化させている。今回 は、現在量産が始まっている、Siインターポーザーの評価技術に ついて紹介する。デバイスとしては、Chip on Wafer on Substrateのタイプであり、これは、複数の異なる機能を持った SiチップをSiウェハ上に搭載し、その後、Substrate 上に実装す る工程をへる。第6図、第7図に、Chip on Waferの接合部を、

# Technical Report A 次世代半導体を支える3D実装技術とその評価法

第8図に、Wafer on Substrateの接合部および、Wafer 中の 貫通電極(Through Silicon Via: TSV)部の断面SEM観察 結果を示す。

第6図に広域断面加工を行い、2.5D実装パッケージの光学 顕微鏡観察した結果を示す。広い範囲でバンプの断面を出すこ とができており、数多くのバンプに対して、接合の良、不良を確認 することができる。第7図がバンプ接合部の拡大図であるが、 Chip on Wafer接合部が、20µm前後のCu バンプをはんだ 接合したものであることがわかる。Snベースのはんだが、Cuバン プと反応して合金を形成し、その合金でバンプ間が接合されてい ることがわかる。接合の評価においては、バンプの位置ずれ、はん だの量ともり方、合金層の成長度合いなどの情報が得られる。特 にバンプのずれはブリッジを誘発する可能性が考えられ、重要な 観察ポイントである。また、アンダーフィル材の充填具合や、フィ

ラーの偏り具合なども明瞭に観察することができ、新しい充填材 料の評価などにも有効である。

第8図に、Wafer on Substrateのバンプ接合部の拡大を示 す。WaferがSiインターポーザーの機能を持つが、写真の上側 に再配線層を持ち、TSVでウェハ下側のCuバンプと接続し、 Substrateとはんだボールで接合されている。この断面SEM観 察により、TSVの出来栄え、Cuバンプとの接続の良・不良、はん だボールのつぶれ具合などの評価が可能である。今回観察した 部位においては、TSVとCuバンプ接合部において、前述した微 細VOIDが多く認められ、長期接続信頼性の点で懸念が残る。

# 第8図 Wafer on Substrate 接合部の拡大観察 反射電子像(組成像) 反射電子像(組成像) Cuバンフ TSV. はんだボール 観察倍率:×500 観察倍率:×1,500

# A-4 ハイブリットボンディング製品の密着性評価

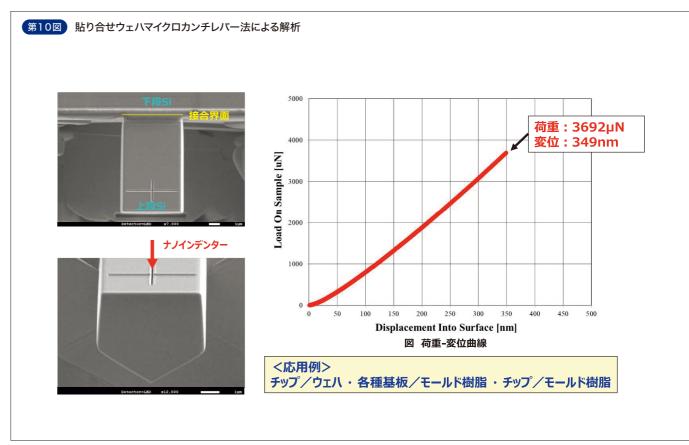

貼り合わせウェハ界面の密着性評価の手法として、Double Cantilever Beam Test(DCB法)が主流であるが、DCB法で は、ウェハの周辺部しか測定できないといったデメリットがある。

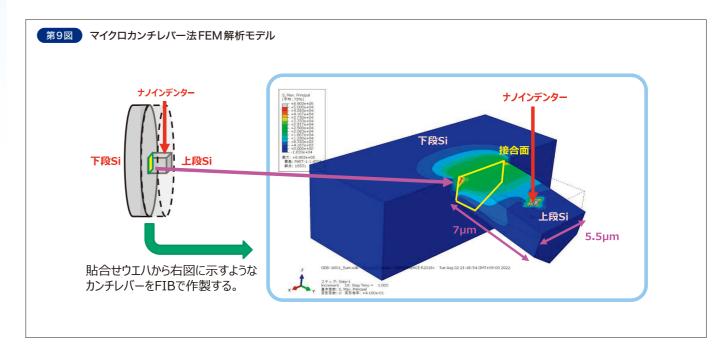

本稿で紹介するマイクロカンチレバー法を第9図に示す。 FEM解析モデルであらかじめ想定されたウェハ界面で、最大応 力が働くようなマイクロカンチレバーサンプルをFocused Ion Beam (FIB) 加工により任意の場所に作製する。作製したレ バー先端部をナノインデンター圧子で押し込んだ際に、レバーが 破壊した時の曲げ応力を求めることで接合強度を評価する手法 である。本手法の最大のメリットは評価位置を自由に選択できる ことであり、ウェハの面内ばらつきなども評価可能である。

第10図は評価の一例である。この事例では荷重約3700µN で破壊した。

本試験方法は、チップ貼り合わせ界面のみならず、さまざまな 接合界面や微細な構造体での応用が期待される。

本稿では3D実装された半導体部品の評価、解析技術の一端を紹介した。チップを垂直方向に積み上げる3D実装や、さまざまな チップを平面方向に配置する2.5D 実装などの、チップレット技術の開発では従来の後工程の概念をくつがえし、前工程の技術を融合 させたプロセスが行われる。そこには、さまざまな接合技術がもちいられており、信頼性の担保のために、その評価を正しく行うことが求め られ、半導体部品の高集積率化、微細化にともない、製品の評価に対するお客様のニーズはますます高まっている。このようなご要望に お応えできるよう、分析・解析技術のさらなる高度化、新規解析技術のメニュー化を図り、社会に貢献していきたいと考えている。